What are Least-Impedance Return Paths?

In printed circuit board (PCB) design, least-impedance return paths refer to the routes that electrical current follows as it returns to its source (such as ground or power) which offer the least resistance or impedance. Current always seeks the path of least resistance. By designing your PCB layout such that the return paths for signals follow the shortest, most direct routes with minimal impedance, you can greatly improve the signal integrity and EMC performance of the board.

Why are Return Paths Important in PCB Design?

The return paths that current follows are critical to PCB performance for several reasons:

- Minimizing loop area: A smaller loop area between a signal and its return path reduces inductance and electromagnetic emissions

- Reducing impedance: Lower impedance in the return path means the current can flow back to its source more easily

- Avoiding discontinuities: Maintaining a continuous, unbroken reference plane for return current prevents issues like ground bounce and EMI

Failing to provide low-impedance return paths can lead to all sorts of signal integrity and EMC headaches. High-speed digital signals may have excessive noise, overshoot/undershoot, or crosstalk. Sensitive analog circuits can pick up interference. The board may fail radiated emissions testing.

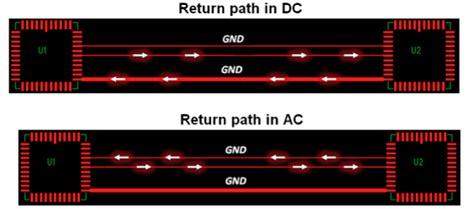

How Current Flows in a PCB

To design effective return paths, it’s important to first understand how current actually flows through conductors in a PCB. At DC and low frequencies, current spreads out and flows through the bulk of the conductor’s cross-sectional area, seeking the path of least resistance.

However, at high frequencies, current flow is constrained by two key effects:

1. Skin effect: Current flows primarily on the surface of the conductor

2. Proximity effect: Current concentrates on the side of the conductor closest to the return path

Due to the skin effect and proximity effect, high frequency currents tend to follow the path of least inductance rather than least resistance. This means the return current will hug as close to the signal trace as it can, rather than spreading out through the entire reference plane.

The return current density is highest directly underneath the signal trace, and it decays exponentially with distance from the trace:

| Distance from Signal Trace | Return Current Density |

|---|---|

| 0 (directly under trace) | 100% |

| 1 x trace width | 60% |

| 3 x trace width | 10% |

| 10 x trace width | ~0% |

As you can see, the vast majority of the return current flows within 1-3 trace widths of the signal. Very little current (<1%) flows more than 10 trace widths away.

Transmission Line Effects

At high frequencies (typically >50 MHz), PCB traces start behaving less like simple conductors and more like transmission lines. A transmission line is a conductor suspended over a reference plane, with a defined characteristic impedance based on the geometry and materials involved.

For proper transmission line behavior and impedance control, it’s critical to provide an uninterrupted reference plane underneath the entire length of the signal trace to carry the return current. Any break in the reference plane, such as a slot or split, forces the return current to find another path, which can cause reflections and EMI issues.

Designing Least-Impedance Return Paths

Now that we understand how high frequency current wants to flow, let’s look at some specific PCB design techniques to ensure signals have low-impedance return paths available:

Provide Continuous Reference Planes

The most fundamental requirement for good return paths is to provide continuous reference planes on adjacent layers to all signal layers. Ideally, each signal layer should have a dedicated reference plane, either ground or power, on the next layer above or below it.

Avoid splitting or slotting reference planes whenever possible. If you must have a break in the plane, such as for a high-current component that requires its own local plane, try to route signals over the unbroken sections of the plane. If a signal must cross a break, place stitching capacitors along the break to provide a low-impedance path for high frequency current to jump the gap.

Minimize Signal Return Path Lengths

Recall that return current wants to flow as close to the signal trace as possible. Therefore, the lowest impedance return path is usually a direct route on the nearest reference plane underneath the signal. Whenever possible, route signals over continuous sections of reference plane, avoiding any slots, splits, or holes that the return current would have to go around.

Also consider the return path length when switching reference planes, such as from a ground plane to a power plane. Changing reference planes forces the current to find a new return path, often through decoupling capacitors or stitching vias. Place decaps and vias close to the signal via to minimize the return path length.

Use Ground Fills

On layers without a continuous reference plane, provide copper fills connected to ground on the same layer and stitch them to the main ground plane with vias. This gives high frequency return currents more paths to flow back to ground.

Make sure to stitch ground fills at least every 1/20th of a wavelength (λ/20) at the highest frequency of concern. For example, a 2.4 GHz signal has a wavelength of 125 mm in FR4, so vias between ground fills and planes should be no more than 125/20 ≈ 6 mm apart.

Beware of Unintentional Inductance

Any conductor that carries current, even a ground or power connection, has some finite inductance. At high frequencies, what seems like a low-impedance ground path at DC may actually have significant impedance due to this inductance. A few pH of extra inductance can make a big difference.

To minimize unintentional inductance in ground connections:

– Mount decoupling capacitors as close to device power pins as possible

– Connect grounds directly to planes with wide, short traces and multiple vias

– Avoid daisy-chaining ground connections from component to component

– Provide ground fills near components and high-speed signals

Isolate Noisy Circuits

Some components, like switching power supplies, have very noisy return currents that can corrupt ground and power planes if not isolated. It’s often best to give these circuits their own local reference planes and route them on separate layers from sensitive signals. Tie the noisy local ground back to the main PCB ground at a single point to avoid ground loops.

Analyzing and Optimizing Return Paths

Fortunately there are several PCB layout tools available that can help analyze and optimize return path impedances. Here are a few techniques:

Return Path Viewer

Many PCB layout programs have a return path viewer that graphically shows the path that current will take through power and ground nets. This lets you easily visualize if your signals have a continuous, low-inductance return path available.

The return path viewer can highlight potential problems like:

– Signals crossing reference plane splits or slots

– Unconnected ground fill areas on the same layer as signals

– Overly long return paths due to improper plane assignments or decoupling placement

Via Inductance Extraction

Vias are often a significant source of inductance in a high-speed signal’s return path. Even through-hole vias have a non-negligible inductance, typically 1-2 nH depending on the via length and barrel/pad size.

Some PCB tools can extract the estimated partial inductance of signal and ground vias based on the geometry and stack-up. Comparing the inductance of different grounding schemes (such as nearby GND vias vs. local ground fill stitching) can help you choose the optimal return path routing.

Ground Fill Stitching Checks

For ground fills to be effective high-frequency return paths, they need to be stitched to the main ground plane with enough vias. Many PCB tools have checks or rules to ensure ground fills are properly stitched, based on the spacing between stitching vias and the highest frequency of interest.

Running a check for unstitched ground fills can reveal areas where high-frequency return currents may be impeded, helping you spot potential signal integrity issues before they cause problems.

FAQ

What is the difference between least-resistance and least-impedance return paths?

At low frequencies, current follows the path of least DC resistance, spreading out through the bulk of conductors. At high frequencies, current follows the path of least AC impedance, concentrating on surfaces and seeking the shortest loop area. Impedance is usually dominated by the inductive reactance, so least-impedance paths are those that minimize loop inductance.

How far from a signal trace does the return current actually flow?

The return current density is highest directly under the signal trace and drops off exponentially with distance. As a rule of thumb, about 90% of the return current flows within 3x the trace width of the signal. At 10x the trace width away, there is near-zero current flowing.

Why are slots and splits in reference planes bad?

Splits in reference planes force return currents to flow around the discontinuity, making the return path longer and higher impedance. At high frequencies, return currents want to stay as close to the signal as possible. Slots and splits make this impossible, so some of the return current reflects back, causing signal integrity and EMI issues.

How can I minimize ground inductance near components?

To minimize the inductance of component ground connections, mount decoupling capacitors close to component pins and connect them to the reference planes with short, wide traces and multiple vias. Also stitch any local ground fills or pours near the component to the main PCB ground plane with closely-spaced vias.

What is the best way to isolate noisy digital currents from sensitive analog signals?

Partition the PCB layout so noisy digital circuitry has its own local ground plane, separate from the analog ground and power planes. Route sensitive analog signals on different layers than digital signals and use ground fills and stitching vias to provide low-impedance analog return paths. Only connect the analog and digital ground nets at a single point to avoid ground loops.

No responses yet