Introduction to DDR2 Signal Integrity

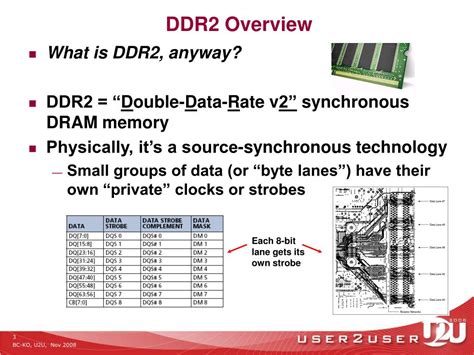

DDR2 (Double Data Rate 2) is a type of synchronous dynamic random-access memory (SDRAM) that has been widely used in computer systems since its introduction in 2003. DDR2 offers several advantages over its predecessor, DDR, including higher clock speeds, lower power consumption, and improved signal integrity. In this article, we will focus on the signal integrity aspects of DDR2 800, a popular variant of DDR2 that operates at a data rate of 800 MT/s (mega transfers per second).

What is Signal Integrity?

Signal integrity (SI) refers to the quality of electrical signals in a system. In the context of DDR2, signal integrity is critical for ensuring reliable data transfer between the memory controller and the DDR2 SDRAM chips. Poor signal integrity can lead to data corruption, system instability, and reduced performance.

Factors Affecting DDR2 Signal Integrity

Several factors can impact the signal integrity of a DDR2 800 interface:

-

PCB layout: The physical layout of the printed circuit board (PCB) can significantly affect signal integrity. Proper routing, impedance control, and signal isolation are essential for maintaining signal quality.

-

Trace length matching: To ensure synchronous data transfer, the trace lengths between the memory controller and the DDR2 SDRAM chips must be carefully matched. Mismatched trace lengths can introduce timing skew and degrade signal integrity.

-

Signal reflections: When a signal encounters an impedance discontinuity, such as a connector or a via, a portion of the signal energy is reflected back towards the source. These reflections can cause signal distortion and reduce the eye opening, making it harder for the receiver to correctly interpret the data.

-

Crosstalk: Crosstalk occurs when a signal on one trace induces unwanted voltage on a neighboring trace. This can lead to signal distortion and reduced noise margin.

-

Power integrity: A clean and stable power supply is essential for maintaining signal integrity. Noise on the power rails can couple into the signal traces and degrade signal quality.

Designing for DDR2 800 Signal Integrity

To ensure optimal signal integrity in a DDR2 800 design, several best practices should be followed:

PCB Layout Guidelines

-

Controlled impedance: The characteristic impedance of the signal traces should be carefully controlled to match the impedance of the DDR2 SDRAM and the memory controller. This is typically achieved by adjusting the trace width, thickness, and spacing relative to the reference plane.

-

Trace routing: Signal traces should be routed as straight as possible, with minimal bends and vias. When bends are necessary, they should be smooth and gradual to minimize reflections.

-

Signal isolation: To reduce crosstalk, sensitive signal traces should be isolated from each other and from other high-speed signals. This can be achieved through proper spacing, shielding, and the use of ground planes.

-

Decoupling capacitors: Adequate decoupling capacitors should be placed close to the DDR2 SDRAM chips and the memory controller to provide a low-impedance path for high-frequency noise and to stabilize the power supply.

Trace Length Matching

To ensure synchronous data transfer, the trace lengths between the memory controller and the DDR2 SDRAM chips must be matched within a specific tolerance. The maximum allowable trace length mismatch depends on the data rate and the signal rise time. For DDR2 800, the typical trace length matching tolerance is around ±50 ps (picoseconds).

Several techniques can be used to achieve trace length matching:

-

Serpentine routing: If a trace is too short, it can be lengthened by adding serpentine shapes to the route. This increases the trace length without affecting the overall signal path.

-

Delay lines: If a trace is too long, a delay line can be added to the shorter traces to match the length of the longest trace. Delay lines are specially designed serpentine structures that provide a known amount of delay.

-

Fly-by routing: In a fly-by topology, the memory controller is connected to the DDR2 SDRAM chips in a daisy-chain fashion. This ensures that the trace lengths are naturally matched, as the signals travel the same distance to reach each SDRAM chip.

Signal Termination

To minimize signal reflections and improve signal quality, proper termination techniques must be employed. The two main termination strategies for DDR2 are:

-

On-die termination (ODT): ODT is a feature built into DDR2 SDRAM chips that allows the termination resistors to be dynamically enabled or disabled. When enabled, the ODT resistors provide a matched impedance load to the signal traces, reducing reflections.

-

Fly-by termination: In a fly-by topology, the termination resistors are placed at the end of the signal chain, after the last SDRAM chip. This provides a matched impedance load to the signals, minimizing reflections.

Simulation and Verification

Before finalizing a DDR2 800 design, it is essential to perform signal integrity simulations to verify that the design meets the required performance criteria. Several tools are available for this purpose, such as:

-

IBIS (Input/Output Buffer Information Specification) models: IBIS models provide a behavioral description of the input/output buffers of the DDR2 SDRAM and the memory controller. These models can be used in signal integrity simulations to predict the performance of the interface.

-

SPICE (Simulation Program with Integrated Circuit Emphasis) models: SPICE models provide a detailed, transistor-level description of the DDR2 SDRAM and the memory controller. These models are more accurate than IBIS models but require more computational resources.

-

Full-wave electromagnetic (EM) simulations: Full-wave EM simulations can be used to analyze the effects of the PCB layout on signal integrity. These simulations take into account the physical properties of the PCB, such as the Dielectric constant and the conductor losses.

Once the design has been verified through simulations, it is important to perform physical measurements on the actual PCB to validate the simulation results. This can be done using high-speed oscilloscopes, time-domain reflectometers (TDRs), and vector network analyzers (VNAs).

DDR2 800 Signal Integrity Challenges and Solutions

Despite the best practices outlined above, achieving optimal signal integrity in a DDR2 800 design can be challenging. Some common issues and their solutions are:

Intersymbol Interference (ISI)

Intersymbol interference occurs when the energy from one symbol (bit) spills over into adjacent symbols, causing signal distortion. ISI is more pronounced at higher data rates, such as DDR2 800, due to the reduced bit period and the increased impact of trace losses and reflections.

To mitigate ISI, several techniques can be employed:

-

Equalization: Equalization techniques, such as pre-emphasis and de-emphasis, can be used to compensate for the frequency-dependent losses in the signal path. Pre-emphasis boosts the high-frequency components of the signal at the transmitter, while de-emphasis attenuates the low-frequency components at the receiver.

-

Forward error correction (FEC): FEC is a technique that adds redundant information to the transmitted data, allowing the receiver to detect and correct errors caused by ISI and other noise sources.

-

Adaptive voltage and timing control: By dynamically adjusting the voltage and timing of the DDR2 signals, the impact of ISI can be minimized. This can be achieved through the use of on-die termination (ODT) and dynamic on-die termination (DODT) features.

Power Supply Noise

Power supply noise can couple into the DDR2 signal traces, causing signal distortion and reducing noise margin. To minimize the impact of power supply noise, several strategies can be employed:

-

Decoupling capacitors: As mentioned earlier, adequate decoupling capacitors should be placed close to the DDR2 SDRAM chips and the memory controller to provide a low-impedance path for high-frequency noise.

-

Power plane splitting: Splitting the power plane into multiple domains can help isolate the noise generated by different components. For example, the DDR2 SDRAM chips can be placed in a separate power domain from the memory controller and other high-speed devices.

-

Ferrite beads: Ferrite beads can be used to suppress high-frequency noise on the power supply lines. These components act as a high-impedance barrier to high-frequency noise while allowing DC and low-frequency currents to pass through.

Crosstalk

Crosstalk between adjacent signal traces can cause signal distortion and reduce noise margin. To minimize crosstalk, several techniques can be employed:

-

Trace spacing: Increasing the spacing between adjacent signal traces can reduce the coupling between them. The optimal spacing depends on the trace geometry, the dielectric constant of the PCB material, and the signal rise time.

-

Shielding: Placing a grounded trace or plane between adjacent signal traces can help shield them from each other, reducing crosstalk.

-

Differential signaling: Using differential signaling, such as in the case of the DDR2 data bus (DQ), can help cancel out the effects of crosstalk. In a differential pair, the two signals are routed together and have equal and opposite voltage swings, causing the induced crosstalk to cancel out.

DDR2 800 Signal Integrity Measurement and Debugging

Once a DDR2 800 design has been fabricated, it is essential to perform physical measurements to verify the signal integrity and to debug any issues that may arise. Several tools and techniques can be used for this purpose:

Oscilloscope Measurements

High-speed oscilloscopes can be used to measure the voltage and timing of the DDR2 signals. Key parameters to measure include:

-

Eye diagram: An eye diagram is a composite view of multiple signal transitions overlaid on top of each other. It provides a visual indication of the signal quality, including the eye opening (width and height), jitter, and noise.

-

Rise and fall times: The rise and fall times of the DDR2 signals should be measured to ensure they meet the specification. Excessive rise and fall times can indicate issues with the signal path, such as excessive capacitance or trace losses.

-

Overshoot and undershoot: Overshoot and undershoot occur when the signal exceeds or falls below the nominal voltage level, respectively. Excessive overshoot and undershoot can cause signal distortion and reduce noise margin.

Time-Domain Reflectometry (TDR)

Time-domain reflectometry is a technique used to analyze the impedance characteristics of a signal path. In TDR, a fast rise time pulse is sent down the signal path, and the reflections are measured using an oscilloscope. By analyzing the timing and amplitude of the reflections, the impedance discontinuities in the signal path can be identified and located.

TDR is particularly useful for debugging issues related to trace impedance, such as:

-

Impedance mismatches: If the characteristic impedance of a trace does not match the impedance of the source or the load, a portion of the signal energy will be reflected back, causing signal distortion. TDR can help identify the location and magnitude of the impedance mismatch.

-

Vias and connectors: Vias and connectors can introduce impedance discontinuities in the signal path. TDR can be used to characterize the impedance of these components and to optimize their design for better signal integrity.

Vector Network Analyzer (VNA) Measurements

A vector network analyzer is a tool used to measure the frequency-dependent characteristics of a signal path. VNAs can measure the scattering parameters (S-parameters) of a network, which describe how the network behaves in terms of reflection and transmission of signals.

VNA measurements can be used to characterize the frequency response of the DDR2 signal path, including:

-

Insertion loss: Insertion loss is the reduction in signal power as it travels through the signal path. Excessive insertion loss can reduce the signal-to-noise ratio and make it harder for the receiver to correctly interpret the data.

-

Return loss: Return loss is a measure of the amount of signal energy that is reflected back towards the source due to impedance mismatches. A high return loss indicates good Impedance Matching, while a low return loss indicates the presence of reflections.

-

Crosstalk: VNA measurements can be used to quantify the amount of crosstalk between adjacent signal traces. By measuring the coupling between the traces, the effectiveness of crosstalk mitigation techniques can be evaluated.

Conclusion

Designing for DDR2 800 signal integrity requires careful consideration of multiple factors, including PCB layout, trace length matching, signal termination, and power supply noise. By following best practices and using appropriate simulation and measurement tools, designers can ensure reliable and high-performance DDR2 800 interfaces.

As data rates continue to increase, the challenges associated with signal integrity will become more pronounced. Designers must stay up-to-date with the latest techniques and technologies to overcome these challenges and to deliver robust and reliable systems.

FAQs

1. What is the difference between DDR2 and DDR3?

DDR3 is the successor to DDR2 and offers several improvements, including higher data rates (up to 2133 MT/s), lower power consumption, and better signal integrity. DDR3 also uses a lower operating voltage (1.5 V) compared to DDR2 (1.8 V).

2. Can DDR2 and DDR3 be used interchangeably?

No, DDR2 and DDR3 are not interchangeable due to differences in their physical and electrical specifications. DDR2 and DDR3 modules have different notch positions, preventing them from being inserted into the wrong type of socket.

3. What is the maximum data rate supported by DDR2?

The maximum data rate supported by DDR2 is 1066 MT/s, achieved by the DDR2-1066 variant. However, DDR2-800 is more commonly used due to its better signal integrity and compatibility with a wider range of systems.

4. How can I improve the signal integrity of my DDR2 800 design?

To improve the signal integrity of a DDR2 800 design, consider the following:

- Ensure proper PCB layout, including controlled impedance, trace routing, and signal isolation.

- Match trace lengths to minimize timing skew.

- Use appropriate signal termination techniques, such as on-die termination (ODT) and fly-by termination.

- Provide adequate decoupling capacitors to minimize power supply noise.

- Use equalization techniques, such as pre-emphasis and de-emphasis, to compensate for frequency-dependent losses.

5. What tools can I use to measure and debug DDR2 800 signal integrity issues?

Several tools can be used to measure and debug DDR2 800 signal integrity issues, including:

- High-speed oscilloscopes for measuring voltage and timing parameters, such as eye diagrams, rise and fall times, and overshoot/undershoot.

- Time-domain reflectometers (TDRs) for analyzing impedance characteristics and identifying discontinuities in the signal path.

- Vector network analyzers (VNAs) for measuring frequency-dependent characteristics, such as insertion loss, return loss, and crosstalk.

By using these tools and following best practices for signal integrity, designers can ensure reliable and high-performance DDR2 800 interfaces.

No responses yet